基于FPGA 的动态异构实时边缘检测系统

成映彤 张瑞起 王广博 何艺辉 高阳

天津职业技术师范大学 300350

引言

图像和视频处理是当今数字时代使用最广泛的技术之一,如工业制造、智能安防和自动驾驶等都是靠图或像进行处理的行业,边缘检测是图像处理的一个重点。边检指的就是找到图像中对比度较大,并且可以显示出清晰图像边界。只有这样才可以更快、更便捷的找到图像所呈现的目标,并且可以加快后期图像识别及处理的进度,达到减少数据处理的工作量、提高工作速度的目的。

传统方案存在显著瓶颈:CPU/GPU 架构处理 1080P@60fps 视频流,常见的时延都大于 30ms 、功耗 >35W ,难以应用于高速产线或者车载等场景;现有的FPGA 解决方案可以达到较低的时延,但由于仅对单一算法进行固化加速,如果想更换其他算子,则需要将整个芯片的比特流重新烧录,在更换期间会有超过 10 秒的中断时间,因而场景适用性较差。

对于上述的问题,针对所提出的问题进行研究并设计了 FPGA 动态异构加速系统,基于”静态逻辑+可重构模块”架构把预处理和核心算法分开,其中静态区为固定连续运行结构,FPGA 动态区使用部分重配技术实现算法在毫秒级内的切换;同时结合自适应阈值技术和定点化技术增加其复杂场景下的鲁棒性以及硬件利用率。

1 相关技术基础

1.1 FPGA 技术概述

FPGA 是一种基于查找表 (LUT) 结构的可编程逻辑器件,用户通过用硬件描述语言来编程配置其内部的逻辑单元及互连线资源,达到实现某种数字电路的目的。与 ASIC 相比,FPGA 具有开发周期短、成本低、灵活的优点,便于及时快速地作出改变以适应市场的需求。

Xilinx Zynq 系列 FPGA 为异构结构,将 FPGA 逻辑与 ARM 处理器融为一体,PL 端包括逻辑单元、触发器、块RAM、DSP 等硬件资源,适用于并行数据处理;PS端为主控双核 Cortex-A9 处理器,用于系统控制、I/0 外设交互等。基于软硬结合的设计思想,充分发挥了 FPGA 进行并行加速处理以及 ARM 处理器具有通用计算的优势,特别适合于实时图像处理系统的使用。

1.2 边缘检测算法

1.2.1 经典算法原理

Sobel 算子:采用3x3 模板对图像进行水平(Gx)、垂直 (Gy) 方向梯度、梯度幅值和梯度方向的计算,虽然算法比较简单,但是边缘定位的精度较差。梯度幅值,方向.

Canny 算法:包括了四个核心步骤: 高斯滤波( 通过消除噪声)、梯度计算( 使用 Sobel 算子求梯度 )、非极大值抑制 ( 在梯度方向保留局部最大值,细化工件边缘),双阈值检测 ( 强边缘直接保存,弱边缘需要和强边缘相连才能被保存)。

1.2.2 算法优化方向

传统的算法用 FPGA 实现时资源消耗太大、且不具备自适应能力,针对这两个问题进行改进如下 :(1) 自适应阈值,通过对灰度直方图峰谷分析动态修改Thigh、Tlow, 并解决了固定阈值下因光照变化大的情况出现漏检。(2) 定点化设计:将浮点运算转化成16 位定点数,精度损失小于 3% ,节省了 50% 以上 DSP 资源。

2 系统设计

2.1 总体架构

系统采用“采集 - 预处理 - 检测 - 存储 - 显示”的流水线架构,各模块功能如下:

1. 图像采集模块:通过 HDMI 接口接收 1080P@60fps 视频流,经 MIPI CSI-2 IP 核解析为24 位RGB 数据,传输至预处理模块;

2. 数 据 预 处 理 模 块( 静 态 逻 辑 区 ): 实 现 RGB 转 灰Y=0.299R+0.587G+0.114B )与 5×5 高斯滤波,输出8 位灰度图像;

3. 动态可重构检测模块(动态逻辑区):包含 Sobel 与 Canny 算法硬件加速核,通过部分重配置实现算法切换;

4. 数据存储模块:采用 DDR3(双 Bank 设计)缓存图像数据,支持乒乓操作避免算法切换时的数据流中断;

5. 显示输出模块:将边缘检测结果转换为VGA 信号,输出至显示器实时显示。

2.2 硬件设计细节

2.2.1 经典算法原理

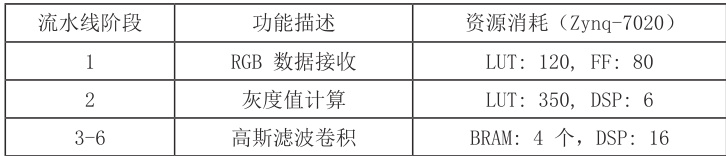

流水线优化:将预处理拆分为 8 级流水线,每级延迟控制在 8ns 以内,吞吐量达 150Mpixel/s(满足 1080P@60fps 需求) )

BRAM 复用策略:高斯滤波需缓存4 行图像数据( 5×5 窗口),采用双端口BRAM 设计,通过地址偏移实现滑动窗口访问。资源计算公式:

2.2.2 动态可重构区设计

动态区划分为两个可重构分区(RP1 :Sobel,RP2 :Canny),通过 AXI 总线与PS 端通信:

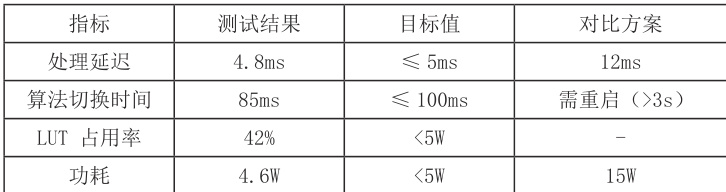

1.Sobel 模块:采用 4 路并行梯度计算,单周期处理 4 个像素,LUT 占用率32% ,延迟 3.2ms ;

2.Canny 模块:8 通道并行非极大值抑制,结合直方图统计实现自适应阈值,LUT 占用率 48% ,延迟 4.5ms ;

部分重配置流程:PS 端通过 ICAP 接口加载分区比特流,切换时间 T 切换Σ=Σ 比特流大小/ 总线带宽 + 初始化时间,经优化后 ⩽100ms 。

2.3 软件控制流程

PS 端 ARM 核运行 Linux 系统,通过设备树配置FPGA 硬件,控制逻辑如下:

1. 系统初始化:加载静态区比特流,配置HDMI/CSI-2 接口;

2. 算法选择:接收上位机指令(UART/ 以太网),确定启用 Sobel 或 Canny算法;

3. 动态重构:若切换算法,PS 端先将当前帧数据写入 DDR3 Bank1,再加载新算法比特流至动态区,完成后从 Bank2 读取数据继续处理;

4. 结果输出:将边缘检测图像通过VGA 驱动显示,并存储至SD 卡。

3 实验与结果分析

3.1 测试环境

硬 件 平 台 :Xilinx Zynq-7020 开 发 板(XC7Z020-1CLG484C),OV7725 摄像头(1080P@60fps),Tektronix MDO3024 示波器 ;软件工具 :Vivado 2022.1,Petalinux 2022.1,MATLAB 2023a ;测试数据集:BSDS500(标准边缘检测数据集)、工业PCB 图像。

3.2 性能指标测试

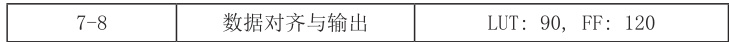

3.2.1 实时性与资源消耗

3.2.2 检测精度验证

4 结语

本研究基于“静态逻辑 + 可重构模块”的设计思路,提出了一种毫秒级快速切换算法的动态异构边缘检测系统,并结合自适应阈值和定点化优化,在1080P@60fps 场景下,达到了 ⩽5ms 延迟、<5W 功耗的核心指标要求,成本仅相当于国外同类产品的 20% 。未来将添加国产 FPGA( 高云 GW5A) 的适配扩展以及添加基于深度学习边缘检测算法可重构的后处理功能来增强鲁棒性。

参考文献:

[1] 祁佳 , 刘紫燕 . 实时图像双边缘检测算法及 FPGA 实现 [J]. 电视技术 ,2014,38(03):64-65+85.DOI:10.16280/j.videoe.2014.03.038.

[2] 王宜聪 . 基于 FPGA 的视频图像边缘实时检测系统设计 [D]. 大连理工大学 ,2020.DOI:10.26991/d.cnki.gdllu.2020.002696.

[3] 胡雪梅 , 吴占敏 . 基于 FPGA 的含噪图像边缘检测系统的设计与实现 [J].电子作 ,2023,31(21):112-115.DOI:10.16589/j.cnki.cn11-3571/tn.2023.21.020.

[4] 徐志辉 , 和晓军 . 基于快速中值边缘检测系统的 FPGA 实现 [J]. 通信与信息技术 ,2024,(05):29-34.

资 助 项 目 :2025 年 市 级 大 学 生 创 新 创 业 训 练 计 划 ( 项 目 编 码:X2025100660110)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)