高可靠性芯片接口防护技术

傅懿斌

上海顺久电子科技有限公司

引言:

现代 CMOS 集成电路工艺从原有的微米、亚微米、深亚微米到目前最先进的纳米级,栅氧厚度、PN 结深度、线间距等物理尺寸都大幅度下降,这些物理结构承受的电场强度也逼近物理极限,导致芯片上的半导体元器件变得越来越脆弱,严重恶化芯片的可靠性 [1-2]。因此,集成电路的防护问题也越发受到国内外产业界和学术界的重视。本文采用芯片被动防护技术和主动防护技术,并且优化了器件结构,通过 testkey 的实测数据,优化器件尺寸,显著提高芯片接口的可靠性。

一、芯片被动防护技术

(一)静电防护与浪涌防护

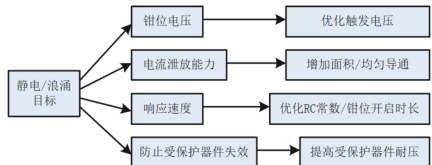

静电防护与浪涌防护方面,静电 ESD 模型主要分为 HBM 人体模型、MM 机器模型、CDM 充电器件模型和系统级 ESD 模型 IEC61000-4-2,浪涌模型遵循IEC61000-4-5。其中,HBM 人体模型测试通过模拟人体带电后接触电子元器件或设备时发生的静电放电事件,使用标准 100pF 电容和 1.5kΩ 电阻,评估被测器件在遭受此类静电冲击时的耐受能力和可靠性;MM 机器模型测试则模拟金属工具或自动化设备带电接触器件(电容更大为 200pF ,电阻很小接近 0Ω,放电更快更严苛)的情况;CDM 充电器件模型测试模拟器件自身在生产、运输过程中因摩擦感应带电,然后接触导体(如工作台、人手)时发生的放电(更接近真实失效机理,上升时间极快 <1ns);IEC61000-4-2 系统级静电放电抗扰度测试评估电气和电子设备在遭受来自操作者或邻近物体的静电放电时,其功能性和性能的抗干扰能力,重点测试设备在放电期间和之后能否维持其预定功能或在可接受的时间内恢复功能,而非设备是否会损坏(虽然可能发生);IEC61000-4-5 系统级芯片级的浪涌测试则评估电气设备和电子系统遭受瞬态过电压后,是否产生永久性功能失效或者器件损坏。因此,在芯片被动防护设计中需充分考虑各种失效情况,明确静电与浪涌防护目标,逐项优化设计参数,保证通过各项测试标准。

图1 :静电/ 浪涌防护设计流程

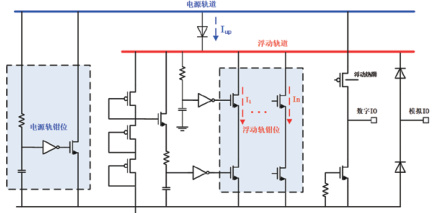

其中静电 / 浪涌防护电路结构如图,分别设计电源轨道和浮动轨道两组电流泄放通路,数字 IO 和模拟 IO 分别采用 GGNMOS 结构和二极管结构进行防护[3],分别达到节省面积和减小寄生的效果。由于采用浮动轨道放电架构,数字IO 和模拟IO 均可支持防倒灌功能 [4]。

图2 :静电/ 浪涌防护电路架构

(二)半导体器件选择

在芯片静电、浪涌防护设计中,选择合适的半导体器件至关重要,常用器件有 MOS 管、二极管、SCR 器件等,需要充分挖掘器件潜力,避免薄弱点导致的溃坝效应。

1、MOS 管

在 ESD 防护结构中常用 2.5VNMOS 管作为 GGNMOS 或 GCNMOS 的电流泄放器件 [4],利用其 snapback 效应,当 NMOS 管的漏端电压上升,漏端到衬底的 PN结发生雪崩击穿,电流流入并抬高衬底电压,开启NMOS 沟道下方寄生三极管 [5],形成ESD 泄放电流,迅速降低结点电压,对电压进行钳位,保护芯片内部器件。

2、二极管

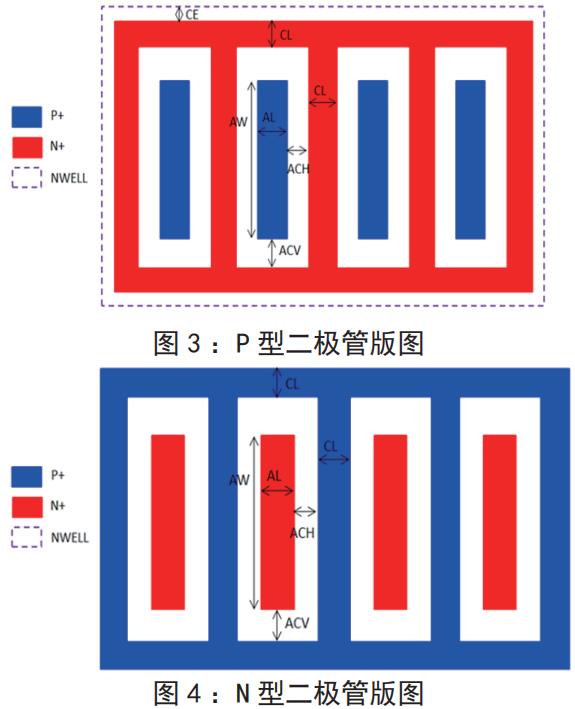

二极管作为常用 ESD 防护器件,通过半导体工艺中的 P 型二极管和 N 型二极管,利用其单向导通特性,分别对正向和负向ESD 电流进行定向引导并泄放,达到保护芯片内部器件的目的。相比于利用 MOS 管进行 ESD 电流泄放的结构,具有寄生电容小、钳位电压低等优点 [6]。在 testkey 中设计了不同尺寸的 P 型二极管和N 型二极管,测试二极管在大电流下的导通和失效数据。

3、LDMOS 器件

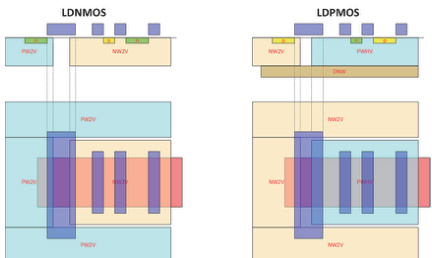

针对芯片最易损坏的接口 IO 电路,在 ESD 事件发生时,被保护器件需要比 ESD 保护电路具有更高的失效点,避免出现 ESD 保护电路尚未损坏,但是被保护器件先失效的情况出现。因此在接口 IO 电路中采用了 LDMOS 器件,利用工艺制程中的 P 阱、N 阱、深 N 阱、P +、N +和浮栅等结构,设计了具有高耐压特性的和LDPMOS 和LDNMOS 器件,从而达到IO 电路的高可靠性[7]。

图 5 :LDNMOS 与 LDPMOS 的平面与剖面结构

二、芯片主动防护技术

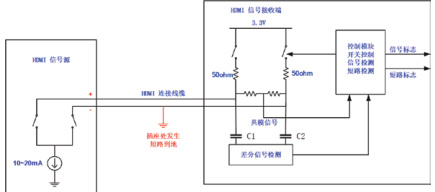

在电子设备中部分芯片引脚端口与整机外部接口直接连接,比如显示器的HDMI 接口会通过PCB 走线直连到芯片引脚端口。用户在使用中会经常插拔线缆,由于设备接口插座存在公差偏大、长期使用后接口松动和用户插偏等原因引起连接短路从而导致芯片与设备的损坏问题。为了解决此类问题,深入研究了此类接口系统,针对直接耦合的 HDMI 接口,如图 6 所示,专门设计短路检测与短路保护系统,可以有效避免芯片接口损坏。

图6 :HDMI 接口连接系统

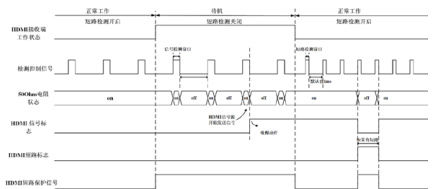

整个短路保护的控制时序如图 7。正常工作状态,检测共模信号,如电压低于设定阈值,判定其为短路状态,关闭终端电阻从而切断短路电流路径,并输出短路标志。发生短路后利用周期性检测,定时打开终端电阻,在窗口期内检测共模信号,判断短路是否消失,如仍处于短路状态,则继续关闭终端电阻,如短路消失,则自动打开终端电阻,保持正常工作状态。控制模块根据检测是否有短路状态和是否有信号输入,产生信号标志和短路标志,并生成待机模式和正常工作模式下的开关控制信号,信号标志和短路标志送到如 CPU、MCU 等进行处理,可进行系统唤醒、提醒用户插座异常要求重新插拔线缆等操作。整个设计考虑了待机模式下的低功耗待机、唤醒检测,和正常工作模式下的短路检测、短路保护,短路消失后的恢复正常工作状态。

图7 :HDMI 接口短路保护控制时序

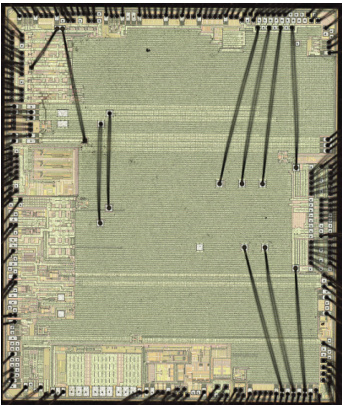

三、实测结果与芯片照片

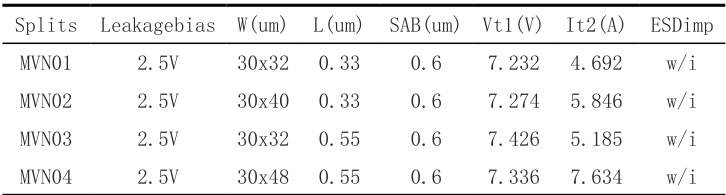

本文在晶合 28nm 工艺上,通过wafer 划片槽中分别设计的NMOS 管、二极管、LDMOS 管的 testkey,并通过 TLP 测量上述元器件的电压 - 电流曲线,明确器件的导通能力与失效电压,为芯片整体防护设计提供可靠依据(如图8、图9)。

图8 :芯片实物照片

图 9 :NMOS 管 TLP 测试曲线

表 1 NMOS 管测试数据

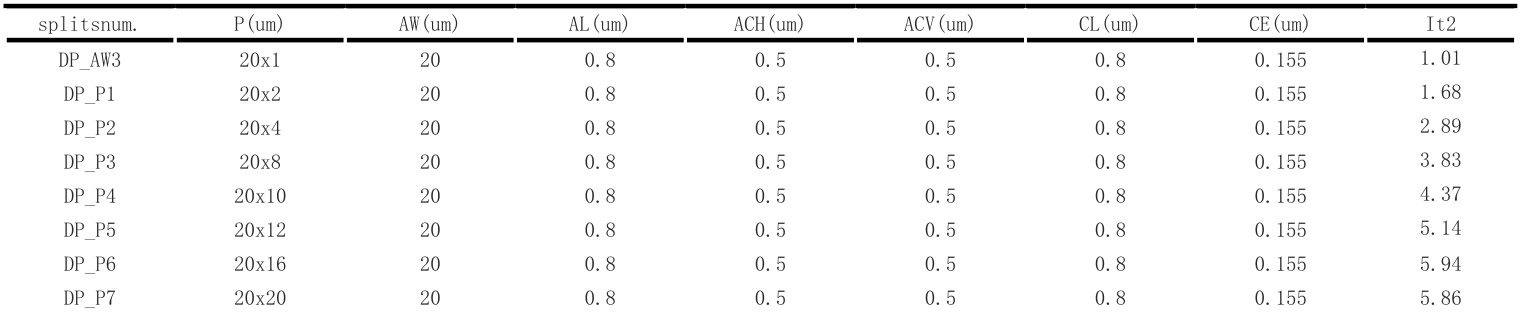

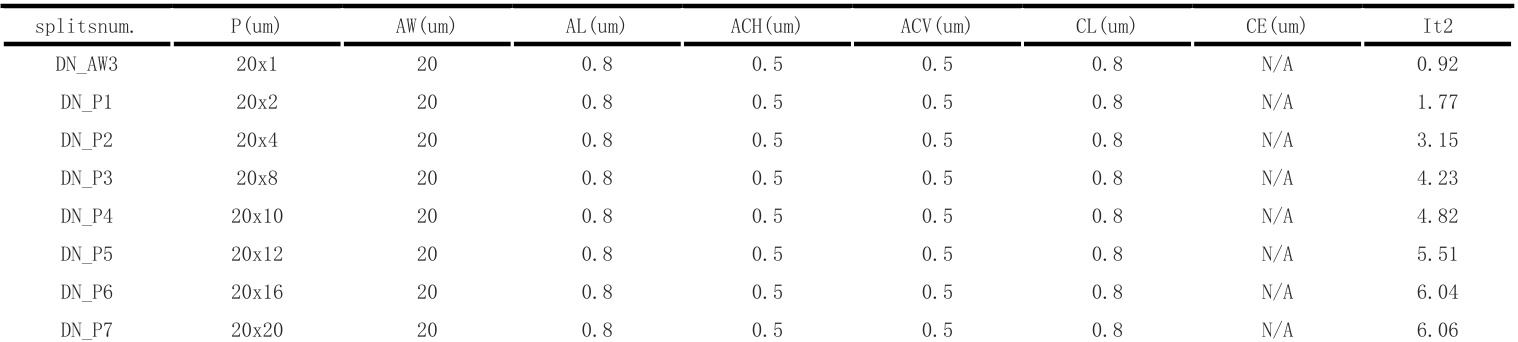

表2 P 型二极管测试结果

表3 N 型二极管测试结果

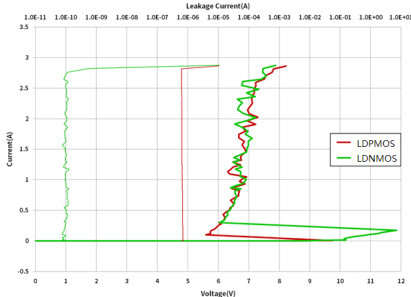

分别测试 LDPMOS 和 LDNMOS 器件的特性,其雪崩击穿触发电压分别为 9.8V和 11.7V,超过 GGNMOSESD 保护结构的雪崩击穿 Vt1 触发电压 7.23V~7 .43V 的范围。LDMOS 管特性测量曲线如图10。

图 10 :LDNMOS 与 LDPMOS TLP 测试曲线

4、结论

本文中芯片采用晶合 28nm1P7M 工艺制造,通过完整的芯片防护设计流程,结合被动保护与主动保护技术,针对器件结构优化设计。芯片在第三方认证机的 ESD 测试中达到 HBM8KV、MM500V、CDM800V 标准,在整机厂系统级测试中,芯片接口引脚达到 IEC61000-4-28KV,IEC61000-4-520V,对系统接口进行短路测试,主动防护响应正确,确保芯片无损坏。通过各类极限测试,证明芯片与整个系统的高可靠性得到显著提升。

参考文献:

[ 1 ] S t e v e n H V o l d m a n . E S D A n a l o g C i r c u i t s a n d D e s i g n [ M ] .JohnWiley&SonsInc,2015.

[2]AjithAmerasekera,CharvakaDuvvury.ESDinSiliconIntegratedCircui ts[M].SecondEdition.England:JohnWiley&Sons,Ltd.,2002:138-148.

[3]Ming-DouKer,Wen-YiChen,Kuo-ChunHsu,“DesignonPowerRailESDClampCircuitfor3.3-VI/OInterfacebyUsingOnly1-V/2.5-VLowVoltageDevicesina130-nmCMOSProcess”inIEEETransactionsonCircuitsandSys tems—I:RegularPapers,vol.53,NO.10,Oct2006,pp.2187-2193

[4] 徐伟,冯全源 . 多指条形 GG-NMOS 结构 ESD 保护电路 [J]. 微电子学,2009(1):60-63.

[5] 鲍剑 , 王志功 . 一种应用于深亚微米 CMOS 工艺的 ESD 保护电路 [J].电子与封装 ,2005,5(8):27-31.

[6] 王大睿 .CMOS 电路中 ESD 保护结构的设计 [J]. 中国集成电路,2007(6):37-41.

[7] 温德通 . 集成电路制造工艺与工程应用 [M]. 北京:机械工业出版社,2018 :44-57.

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)