中低压VDMOS 提升EAS 能力的研究与设计

倪磊 李朴 吴慧敏 全宣羽

西安卫光科技有限公司 陕西西安 710065

引言

VDMOS 器件凭借其高耐压、低损耗、快速开关及高频等特性在电力电子技术领域应用越来越广泛。随着该器件在汽车电子、航空航天等领域更广泛的应用,除了对于效能的考量外,器件的可靠性使用越来越受到重视。对于开关器件,非钳位感性负载下的开关过程会让器件同时承受高电压和大电流,雪崩耐量 EAS 是用来衡量器件对此极端应力的承受情况的重要指标参数。

客户在特定环境下的电源转换中,使用我司产品 17N20 时遇到因过压问题导致器件损坏的现象,判断是该产品的EAS 能力较弱从而导致的器件损坏,该产品的标称雪崩耐量为0.48J,客户需求其他静态参数不变的情况下,提升EAS 能力至0.55J 以上。

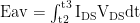

1 典型 EAS 测试原理

雪崩耐量体现了半导体开关器件的过雪崩电流能力,非钳位感性负载开关(UnclampedInductive Switching,UIS)的典型电路结构如下所示:t1 到 t3 的过程为一次 UIS 过程,首先对待测器件的 Gate 施加开启信号,使电感储存能量;之后储存的能量由被测器件进行吸收。器件吸收能量而不损坏的最大能量值为器件的雪崩耐量。对 tav 时间段电流和电压乘积积分可得到器件吸收的能量,即单次雪崩耐量Eav :

图 1 VDMOS 器件 EAS 测试原理图

其中,VDD=50V,L=1.00mH。2 产品失效机理及影响因素

⑴ 失效机理

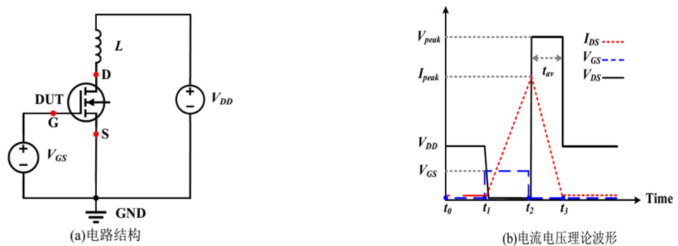

(1)寄生二极管雪崩烧毁:VDMOS 结构中,Body 区与外延之间的存在寄生二极管,如下图 2 :当外接感性负载时,器件关断后漏极电流不会突变,但体内寄生二极管反偏电压瞬间被抬升,进入雪崩状态。流过二极管的大电流及两端高电压会在器件内部产生热量,散热不及时就会导致MOS 过热烧毁失效。

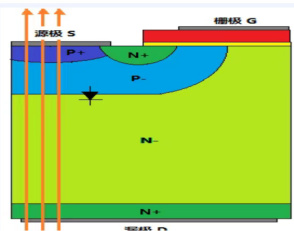

(2)寄生三极管开启:正常情况下,VDMOS 中 RS 两端电压很小(小于正向开启电压),流过的电流几乎为 0 ;但当寄生二极管雪崩击穿时,即雪崩电流足够长并持续足够长时间,就可能激活内部的寄生NPN 双极晶体管( 如下图3),进而引发闩锁效应。一旦发生闩锁效应,MOSFET 内部会形成一个不可控的大电流通道,这不仅会导致功耗急剧增加,还可能因过热而造成永久性损伤。

图2 寄生二极管图例

图3 寄生三极管图例

⑵ 影响EAS 特性的因素

结构设计:不同的MOSFET内部结构设计会影响其雪崩耐受能力。例如,Contact结构问题、

寄生三极管问题,还有较大的芯片面积有助于散热,但同时也增加了寄生电容,影响开关速度。材料特性:硅基 (Si) 与碳化硅 (SiC) 等不同半导体材料因其物理属性差异而表现出不

同的雪崩行为。SiC MOSFET 由于其宽禁带特性,在高温环境下具备更佳的雪崩鲁棒性。外部条件:温度、湿度、周围环境中的电磁干扰等因素都会对实际应用中的EAS 产生影响。

3 EAS 性能优化提升

(1)优化方向

为了不影响其他参数,MOS 设计中通常都是减小 Body 中的横向电阻 RS, 本产品采用Deep body 的注入方式来实现。将原本流程 PSD 层光刻取消,增加 LPSIN spacer 工艺作为沟道处的阻挡层,优化 PSD 层进行普注菜单,增加 P+ 区注入尺寸及深度 , 降低基区电阻Rs,有利于减小器件寄生 NPN 晶体管导通的可能性,提高其抗动态雪崩能力,在满足器件击穿电压、导通电阻的同时,达到用户对EAS 能力应用要求。

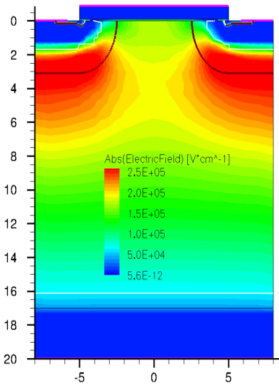

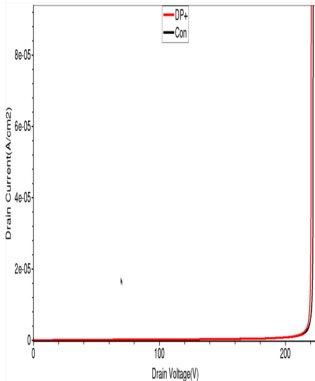

(2)器件仿真结果

将以上设计结果导入二维仿真软件 ISE-TCAD 中进行工艺和器件参数仿真。工艺仿真结果如图 4 所示。 击穿电压仿真结果比对从图 5 可以看出,击穿电压满足产品设计要求,优化前后无明显差异;图6 为导通电阻的仿真结果比对,优化前后无明显差异,且达到设计要求;由图7 EAS 能力仿真结果比,可以看出Deep body 的电流密度与电压随时间的积分即EAS 能力,较工艺优化前有明显的提升,仿真结果满足客户对产品性能的要求。

图4 工艺仿真结果

图5 击穿电压仿真结果比对

图6 导通电阻仿真结果比对

图7 EAS 仿真结果比对

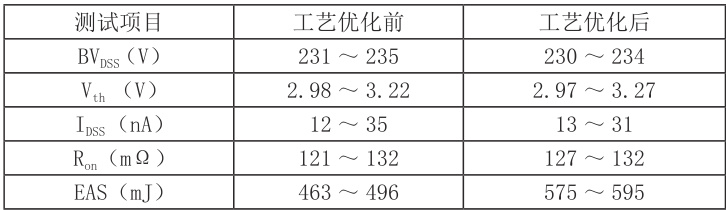

4 实验结果与讨论

对本文设计 18A/200V 器件,通过流片制造以及封装测试,静态参数、EAS 和可靠性均满足要求,测试结果见表1。

表1 测试参数的比较

从参数测试结果可以看出,工艺优化前后产品的基本静态参数无明显变化,而优化后EAS 能力较优化前有明显的提高,大约提升100mJ 左右,满足客户使用要求。

结论

本文通过模拟软件对中低压 200V/18A VDMOS 的导通电阻和反向击穿电压及 EAS 能力进行仿真分析,流片结果数据表明,通过工艺调整增大 P+ 区注入尺寸及深度,降低基区电阻Rs,在其他静态参数不变的情况下,可有效提高器件的抗雪崩能力。

参考文献:

[1] 马万里 , 赵文魁 . VDMOS 的 USI 能力与制造工艺流程的关系 . [J]. 微电子学 ,

2012。

[2] 刘松 , 杨营 . 功率 MOSFET 雪崩能量及雪崩失效分析 [J]. 电子技术应用 , 2016,

42。

[3] 李意 , 尹华杰 , 牟润芝 . 功率 MOSFER 雪崩击穿分析 [J]. 电源技术应用 ,2003。

[4] 徐伯强 . 优化 VDMOS 雪崩能量的研究 [M]. 2009。

[5] 刘松 , 葛小荣 . 理解功率 MOSFET 的 UIS 及雪崩能量 [J]. 今日电子 , 2010(4)。

作者简介:第一作者简介:倪磊(1985-),男工程师,本科,研究方向功率半导体器件研究。

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)