基于RISC-V 的流水线执行效率关键影响因素分析

张帅 李艳 王子健 陈佳

武汉第二船舶设计研究所 湖北武汉 430025 武汉晴川学院 湖北武汉 430204 中国地质大学 湖北武汉 430074

1 基于 RISC-V 的流水线架构

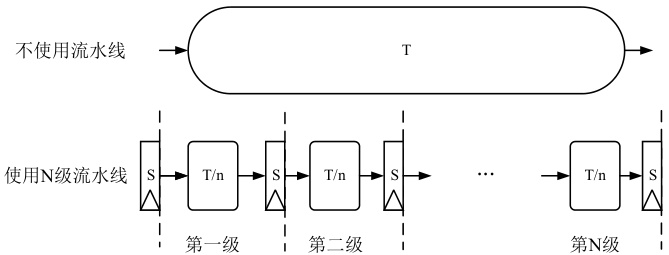

当处理器未使用流水线时,一个周期需要花费时间为 T,频率为1/T。将一个周期需要完成的任务划分为 Πn 级流水线后,一个周期花费时间为“ *T/n+S′′,S 表示流水线寄存器的延时,频率变为 1/(T/n+S) 随着现代半导体工艺的不断升级,S 正在逐渐减小,处理器主频趋于1/(T/n) ,并且 Πn 级流水线之间相互独立,能够并行处理任务,如图 1所示。

图 1 流水线技术对处理器性能影响

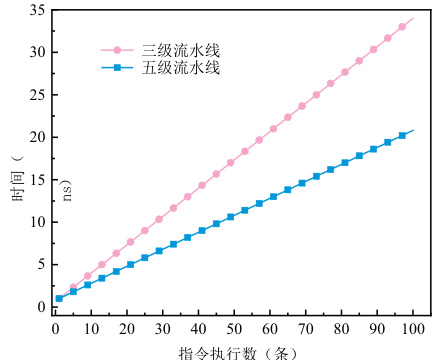

如图 2 所示为 100MHz 频率下五级和三级流水线执行指令所花费的时间随指令数增加的变化情况(忽略流水线寄存器的延时)。

图2 五级与三级流水线指令执行效率对比

可以看出,随着指令执行数的增加,五级流水线平均每条指令所花费的时间与三级流水线之间的差值逐渐增大。在执行 100 条指令后五级流水线所花费的时间仅为三级流水线的 61% 。但是流水线的深度并不是越深越好,流水线的加入会使用额外的流水线寄存器,加大处理器的面积。同时,分支指令预测失败带来的惩罚也会随之加剧。因此,流水线的深度需要综合考虑,对于面向高性能计算这类对性能要求较高的处理器,硬件面积可以次要考虑;而对于低功耗的物联网领域,面对成百上千的节点以及各类特殊的应用场景,此时首要考虑的就是面积。

2 流水线冒险

流水线的加入,使处理器每个阶段之间相互独立,但是指令之间却存在依赖关系或资源冲突,往往会导致流水线的停滞,影响指令的执行效率。这种情况称为冒险,一共可以分为以下三种:

(1)结构冒险:一般发生在多个指令需要使用同一个硬件资源。例如在冯·诺依曼结构的处理器中,指令和数据存储在同一个存储器,通过单一总线与处理器核相连,由不同的地址进行访问。这也导致取指操作与访存操作需要访问同一个存储器,此时就产生了结构冒险,需要对流水线进行暂停等待其中一个操作执行完成后才能执行另一个操作。

(2)数据冒险:又称为数据相关性,一般为指令之间产生的依赖关系,这种依赖关系决定了指令的执行顺序。如果不加以解决,数据相关性可能使流水线发生停顿导致执行效率的下降,数据相关性又分为写后读(Read After Write,RAW)、写后写(Write After Write,WAW)以及读后写(Write After Read,WAR)。

其中写后读一般发生在后续指令需要前序指令的执行结果,而此时前序指令还未执行完成,此时就发生了 RAW 数据相关性;写后写一般发生在两条指令需要写入到同一个寄存器,即后续指令写回的寄存器地址与前序指令相同,而此时前序指令还未执行结束后续指令就要写回(前序指令一般为需要多个周期执行的长指令,如 MUL),此时就发生 WAW 数据相关性;读后写一般发生在一条指令需要写入一个寄存器,而该寄存器之前被另一条指令读取时,即后续指令需要读取的寄存器地址与前序指令将要写入的寄存器地址相同,此时就发生了WAR 数据相关性。

(3)控制冒险:由分支指令导致的冒险,即当处理器无法确定下一条指令地址时所产生的冒险。这是因为分支指令的结果需要等到流水线的后期阶段才能确定,在这之前,分支指令的执行结果是未知的,导致处理器可能执行处于错误路径之上的指令,需要对流水线进行冲刷清除这些指令。

3 分支预测的更新

为保证指令流的连续性,分支预测一般在取指阶段,但更新的阶段却有不同的选择。对于分支指令的方向预测,无论是基于局部历史与基于全局历史的预测方法,在什么时候对分支预测器进行更新都会对预测准确率有一定的影响。这是因为分支指令在执行阶段才能获取实际的跳转结果,而在将结果更新到分支预测器之前,使用的是还未更新的结果对后续分支指令进行预测。分支方向预测器的更新内容一般指历史寄存器以及饱和计数器,以五级流水线为例,更新阶段一般有以下三种:

(1)在流水线的取指阶段进行更新,但往往这是分支指令的结果还没出来,一般采用分支指令的预测结果进行更新;

(2)在流水线的执行阶段进行更新,这个时候分支指令的实际跳转结果已经被计算出来,相比取指阶段的预测结果更加可靠;

(3)在流水线的写回阶段进行更新,这个时候该指令的所有结果均为已经确定的,此时的结果肯定是正确的。

对于在取指阶段进行更新,由于分支指令预测的结果不一定正确,使用该结果进行更新,可能会使后续的指令使用错误的分支历史进行预测。但后续分支指令都处于错误路径,会被流水线冲刷机制抹除,所以即便使用错误的分支历史也没有影响。但是这种方法在预测失败后需要额外的机制对分支历史进行修复,使其恢复到正确的值。

对于在写回阶段进行更新,虽然此时的结果一定正确,但是对于如今各类超标量或深流水线处理器,每周期需要执行多条指令,并且在指令到达写回阶段时,流水线已经涌入了多条指令。其中的分支指令无法及时得到最新的分支历史以及饱和计数器的状态,对于分支预测的准确率有一定的影响。

而在执行阶段进行更新,比写回阶段进行更新要提前许多。对于五级流水线处理器来说,执行与取指之间只间隔两个时钟周期,此时进行更新不会对后续指令使用分支历史进行分支预测照成太大的影响,且此时的结果相对可靠,不需要进行额外的机制对其进行修复。

作者简介:

张帅 (1987-),男,内蒙古巴彦淖尔人,博士研究生,2010 年于武汉大学获得学士学位,2015 年于武汉大学获得博士学位,同年于任职工作,主要从事高速模拟电路设计、RISC-V、数据传输、信号完整性和通信方面的研究。

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)