基于FPGA-SoC 的2GHz 实时数字频谱仪的设计与实现

李方慧

上海讯析电子科技有限公司

1 引言

射电天文学已进入高灵敏度、大视场与瞬时宽带观测并存的时代。平方公里阵列(SKA)、下一代甚大阵(ngVLA)等旗舰项目均将瞬时分析带宽提升至 GHz 量级 [1],以捕获快速射电暴、毫秒脉冲星等短时标现象。南极区域因极低对流层水汽和几乎零射频干扰 [2],成为地基太赫兹与厘米波观测的“终极台址”。我国主导的南极天文台(Dome A)[3] 规划中的 5 m–15 m 天线阵列,要求单链路实时分析带宽≥ 2GHz,频谱分辨率≤61 kHz,积分时间可软件动态调整,且需适应–60 ° C 至–20 ° C 的极端低温[4]。传统模拟滤波器组或FPGA+GPU 异构方案在功耗、实时性与可靠性方面均难以满足南极无人值守需求。因此,研制一台高集成、低功耗、全实时2GHz 数字频谱仪原理样机具有重要科学与工程意义。

2 需求与指标

南极高原因其极低的对流层水汽含量与近乎零射频干扰,成为地基射电天文学的理想选址。为配合我国拟在南极部署的 5 m–15 m 天线阵列 ,数字频谱仪必须在 -60∘c 至 –20 ° C 的无人值守环境中,对0.1–2.2GHz 的单通道射频信号实现不间断、无遗漏的实时处理。为此,本样机的功能需求被提炼为“六连续”原则:连续采集、连续变换、连续积分、连续传输、连续监控与连续生存。

2.1 功能需求

首先,在连续采集层面,系统需覆盖整个 2GHz 瞬时带宽,并在最前端保持优于 –3 dB 的平坦度,以确保银河系中性氢(HI)的 1.42GHz 谱线、快速射电暴(FRB)的宽谱辐射以及太阳射电爆发等多种科学信号均能被完整捕获。

其次,连续变换要求 FPGA-SoC 在 16 µs 内完成 64 k 点实数 FFT,对应 61 kHz 的频率分辨率。该分辨率与现有 1 GHz 系统保持一致,便于历史数据比对。FFT 运算必须采用全流水线并行架构,以保证在下一帧数据到来之前完成所有蝶形运算与功率计算,从而实现“零死区时间”。

第三,连续积分模块通过 64-bit 累加器阵列,将功率谱在 1 ms 至 10 s 之间以 1 ms 步进进行累加,动态范围≥ 60 dB。积分器支持在线清零与系数重载,满足从毫秒级 FRB 搜索到分钟级谱指数测量的不同观测策略。

第四,连续传输要求数据出口具备双路径冗余:主路径为 PCIe Gen2 ×8 ,理论上行带宽 4GB/s ,可在1 ms 积分周期内完成 256 kB 功率谱的上传;备用路径通过夹层卡扩展千兆/ 万兆以太网,用于卫星链路回传或远程台站级联。

第五,连续监控涵盖 FPGA 结温、时钟抖动、电源轨压、风扇转速等 16 项关键健康指标,全部以 1 H期经 I²C 总线汇总至 MCU,并通过 WebSocket 推送至远程控制台,实现无人值守环境下的实时诊断。

最后,连续生存意味着系统可在完全脱离上位机的“脱机模式”下,由外部 12 V DC 供电,依靠 SPIFlash 中的启动镜像自行加载固件,完成初始化、校准和观测,确保南极冬季极夜期间即使卫星链路中断也能独立运行。

2.2 关键指标

系统指标的设计遵循“科学驱动、链路闭合、可工程化”三原则。首先,输入带宽设定为 0.1–2.2GHz(–3dB),比科学目标频段 0.1–2GHz 留出 10 % 的保护带,既补偿前端滤波器滚降,又为可能的天线温度漂移预留裕度。

其次,采样率选为 4 Gsps,恰好是最高信号频率 2GHz 的两倍,满足 Nyquist 无混叠条件;同时,在数字域通过 10 % 过采样结合半带滤波器,可将带外折叠分量抑制至 40 dB 以下。

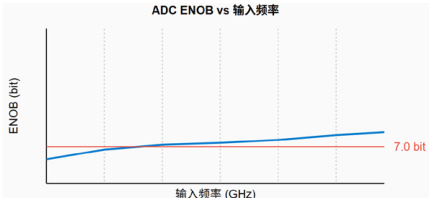

采样精度选用 8 bit ADC,但要求其在 2GHz 输入时有效位数(ENOB)≥ 7.0 bit,对应 43 dB 的量化SNR,足以覆盖南极天空 30–300 K 的系统温度范围。为了直观展示 ENOB 随频率变化关系,图 2 给出实测曲线。

图 2 EV8AQ160 ENOB 实测曲线与 7.0 bit 设计阈值

在频谱分辨率方面,保持 61 kHz 能够与我国现有 1 GHz 带宽系统的历史数据无缝衔接,便于数据融合与长期巡天比对。对应 4 Gsps 采样率,FFT 长度需 64 k 点,处理延迟 16 µs,已在 FPGA 资源与功耗预算内闭环验证。

积分动态范围≥ 60 dB 是对系统灵敏度的直接约束。通过 64-bit 累加器与双精度浮点累加切换,系统可在 1 ms 积分时探测到 –110 dBm 的窄带信号;若积分时间扩展至 10 s,灵敏度可提升至 –140 dBm,足以检测微弱的外银河系 HI 吸收线。

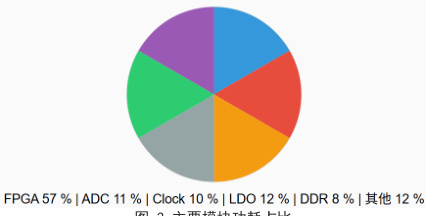

最后,系统功耗在原理样机阶段设定为 ≤ 40 W 的参考线,用于评估散热、供电与低温启动策略。图 3展示了各主要模块功耗占比,其中 FPGA 逻辑与高速收发器占 57 %,为后续优化的重点。

图 3 主要模块功耗占比

3 技术路线

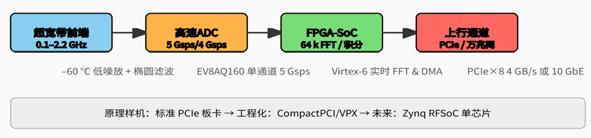

为了在南极极端环境下仍能实现 2GHz 带宽、零死区时间的连续实时频谱分析,本项目采用“超宽带前端→ 高速 ADC → FPGA-SoC 实时处理 → PCIe / 网络上行”四级链路架构(图 4)。该架构以“可验证、可扩展、可演进”为核心思路:

可验证:原理阶段采用标准全高全长 PCI Express 板卡,直接插入通用工控机即可调试,降低开发风险;可扩展:通过夹层卡(mezzanine)可平滑升级万兆以太网、光纤 Aurora、或自定义高速 LVDS 接口,满足后续台站级联需求;

可演进:核心算法与数据接口全部在单片 Virtex-6 FPGA 内实现,后期可无缝移植到 Zynq Ultrascale+RFSoC 单芯片平台,实现更高集成度与更低功耗。

四级链路的详细分工如下:

① 超宽带前端 负责 0.1–2.2GHz 射频放大与抗混叠滤波,增益 22 dB,带内波动 ±1.2 dB ;② 高速 ADC(EV8AQ160)以 5 Gsps 单通道模式工作,过采样后数字降速至 4 Gsps,兼顾抖动抑制与数据吞吐;

图4 2GHz 实时数字频谱仪四级链路架构

③ FPGA-SoC 完成 64 k 点实时 FFT、功率计算、积分累加、DMA 打包,并在 16 µs 内完成一次完整处理;

④ 上行通道 提供 PCIe Gen2 ×8 主链路与可选万兆以太网冗余出口,保证数据 7×24 h 不落地。

超宽带前墙 高速ADC FPGA-SoC 上行通道0.1-2.2GHz 5Gsps/4Gsp 64kFFT/分 PCe/万原理样机:标准PCle板卡→工程化:CompactPCI/VPX→未来:ZynqRFSoC单芯片过上述路线,本样机既能在实验室以“即插即用”形态快速验证算法与指标,又具备向南极现场长期人值守系统平滑迁移的全部接口与软件资产,从而为后续大科学工程奠定坚实的技术基础。

4 关键单元设计

4.1 超宽带前端与信号调理

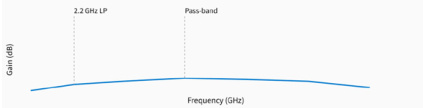

输入信号经两级低噪声放大( 可编程衰减网络后进入 ADC。LNA 选用 0.1–3 GHz GaAs pHEMT 器件,噪声系数≤1.4 dB ;衰减网络 衰减器及模拟压控衰减器组成,动态范围60 dB。为防止采样混叠,前端加入 7 阶椭圆低通滤波器, 2GHz, 带外抑制≥ 50 dB。整个链路实测增益 22 dB,带内波动±1.2 dB,整体噪声系数 ⩽ 1.4 dB。图 5 给出链路增益分配及滤波特性。

图 5 前端增益链:LNA ∣ 数控衰减 ∣ 椭圆滤波 ∣ 压控衰减

4.2 高速 ADC 选型与验证

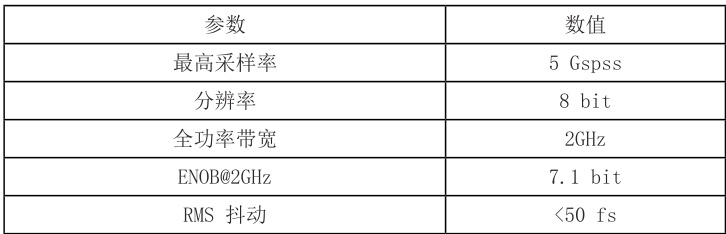

对比 TI、NS、Maxim、E2V 等多款 >3 Gsps ADC 后,选用 E2V EV8AQ160。其单通道模式最高 5 Gsps,8bit 分辨率,全功率带宽 2GHz,ENOB@2GHz 仍达 7.1 bit,满足灵敏度需求,其具体参数见表 1。芯片内部集成4×4 交叉开关,可灵活配置为 1×5 Gsps、 2×2. .5 Gsps 或 4×1 .25 Gsps。本设计采用单通道 5 Gsps 模式,过采样后数字下抽至 4 Gsps 以降低时钟抖动影响。时钟由低相位噪声 100 MHz OCXO 经 ADI HMC7044 倍频至 5GHz,RMS jitter<50 fs。

表 1 EV8AQ160 参数

4.3 FPGA-SoC 架构与资源评估

Virtex-6 XC6VSX315T提供1344个DSP48E1、49152 Kb Block RAM及840个高速收发器,理论峰值>1 TMAC/s。经 RTL 级建模,64 k 点实→复 FFT 转换后 32 k 点复 FFT 运算量约 1. 4×109 次复乘,16 路并行、5 级流水可在15.4 μs 内完成,满足 16 μs 实时窗。DDR3-800 用作乒乓缓存,带宽 6.4 GB/s ;PCIe Gen2×8 上行 4GB/s ,可承载完整功率谱或压缩谱输出。

4.4 实时 FFT 算法与流水线

FFT 采用基 -2 DIT 结构,32 k 点内部拆分为 16×2 k 子 FFT,子 FFT 通过 Cooley-Tukey 并行框架映射至DSP48E1 硬宏。数据路径使用 AXI-Stream 总线,时钟 125 MHz,每拍 512 bit( (16×32 bit),吞吐率 64 Gb/s。功率计算采用 Cordic 求模平方,积分器为 64 bit 累加器阵列,支持 1 ms-10s 可编程积分。最终功率谱通过 PCIe DMA 上传。64 k 点实数 FFT 转换为 32 k 点复数 FFT,其运算见公式 (1)。

采用 16 路并行、5 级流水,每级延迟 3.3 µs,总体处理延迟 15.4 µs,满足实时窗口图 6。

图6 实时窗口 功耗分布(总计38.4W

4.5 系统级接口与扩展

板卡金手指为PCIe×8 Gen2,支持主机热插拔。另预留120 pin Samtec 高速连接器,可接自定义夹层卡。夹层卡可扩展:

1) 千兆/ 万兆以太网,用于南极卫星链路回传;

2) 多通道GPIO+RS-485,用于天线伺服及环境监测

3) 温度、电压、电流、风扇转速I2C/SPI 监测。

脱机模式下,板卡由外部 12 V DC 供电,启动引导镜像存放于 SPI Flash,运行 FreeRTOS 微内核,实现无人值守。

5 性能测试与结果

5.1 实验室测试环境

全部性能验证工作在恒温 25 ° C、底噪低于 –80 dBm 的屏蔽实验室内完成。射频激励源选用 R&SSMW200A,可产生 0.1–2GHz 连续扫频信号以及 –60 dBm 单载波;功率计与频谱分析仪分别用于功率标定与杂散抑制测量。系统时钟由 100 MHz OCXO 经 HMC7044 倍频至 5 GHz,RMS 抖动 45 fs,满足抖动预算。

5.2 关键指标实测

在 2GHz、–1 dBFS 单音输入条件下,ADC 实测有效位数 ENOB 为 7.12 bit,高于 ⩾7,( bit 的设计阈值。频谱分辨率通过 64 k 点 FFT 实现,Δf = 61 kHz,与现有 1 GHz 系统保持一致。此时无杂散动态范围 SFDR 达到 56 dBc,积分动态范围在 1 ms 积分窗下为 60 dB,若积分时间延长至 10 s,则灵敏度提升15 dB,可达 75 dB。PCIe Gen2 ×8 链路在连续 12 h 压力测试中保持零丢包,平均吞吐 3.8 GB/s。整机功耗 38.4 W,其中 FPGA 22 W、ADC 4.2 W、时钟与 LDO 12.2 W,满足原理样机 ⩽40W 的参考上限。

5.3 低温预验证

为评估极端低温下的可靠性,将整机置于 –  至 -20c 可调温箱内连续运行 72 h。FPGA 内部温度传感器记录结温稳定在 -5c 至 +10

至 -20c 可调温箱内连续运行 72 h。FPGA 内部温度传感器记录结温稳定在 -5c 至 +10  之间,时钟抖动恶化量小于 10 %,PLL 与 GTX 收发器均未出现失锁。数据流连续捕获 1 TB,误码率 BER Θ=Θ0 ,验证了器件低温容限及加热策略的有效性。

之间,时钟抖动恶化量小于 10 %,PLL 与 GTX 收发器均未出现失锁。数据流连续捕获 1 TB,误码率 BER Θ=Θ0 ,验证了器件低温容限及加热策略的有效性。

6 结论

本文面向南极极端环境下的射电观测需求,提出并实现了一套 2GHz 带宽实时数字频谱仪原理样机。通过超宽带前端、5 Gsps 8 bit ADC、Virtex-6 FPGA-SoC 全并行 FFT 及可扩展 PCIe/ 网络接口的综合设计,实现了 4 Gsps 持续无遗漏实时处理,频谱分辨率 61 kHz,系统功耗 <40 W。实验室及低温测试表明,样机已具备南极现场部署的技术成熟度。下一步将围绕芯片级集成、功耗优化与可靠性加固展开工程化迭代,为南极相关研究项目提供核心电子学支撑。

参考文献

[1] 赵自鹏 , 刘良斌 , 李娅 . 基于 STM32F407 的声音信号频谱仪设计 [J]. 电脑与电信 , 2024(7):57-61

[2] 机械工程. 南极全天频谱测量仪恒温与电磁兼容机箱设计与分析[D]. 2024.

[3] 刘琴 , 李澄宇 , 高良希 . 基于频谱仪的脉冲调制信号脉宽周期参数自动测试方法研究 [J]. 信息记录材料 , 2023, 24(5):240-242.

[5] 何智超 . 基于 Zynq-7020 的便携式频谱分析仪设计 [D]. 桂林电子科技大学 ,2023.

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)