多路高清视频编解码系统的设计与实现

梁状状

海装驻苏州地区军事代表室 江苏苏州 215151

引言

视频应用正经历由高清往超高清转换的过程。超高清视频提供了更高的分辨率、更高的帧率以及更高的色彩深度, 而目前广泛的 H.264 编码难以对超高清视频进行有效的压缩。H.265 编码技术在 H.264 编码的基础上显著提高了压缩效率,在不改变视频质量的基础上可将视频码率降低一半以上。目前, H.265 的解码技术已经比较成熟,但 H.265 编码由于其计算的高复杂度,可供选择的应用相对较少,且编码效率较低。随着超高清视频的发展,高性能的H.265 编码传输系统的实现已成为当前视频应用领域亟待解决的问题。

本文所采用的 Xilinx 第二代 Zynq 平台的 Zynq UltraScale+ MPSoC EV 系列芯片集成了编解码硬核,可以实现 4K 60 fps 视频的 H.265 同时编解码。并且,该芯片集成了 APU、RPU、GPU 等处理核心以及丰富的可编程逻辑,具有良好的灵活性与可扩展性。在该平台下,通过HLS 工具、reVISON 堆栈等可以快速实现图像处理、机器视觉等算法的硬件加速 , 并且利用FPGA 在通信、运动控制等方面的优势,可以通过单个芯片实现复杂应用。例如,实现无人机的航拍、图传、智能感知、飞行控制等 . 采用 Zynq UltraScale+ MPSoC EV 系列芯片实现编码传输系统相对软件实现方案具有更高的性能与更低的功耗,相比其他硬件实现具有更好的灵活性与扩展性。

1 系统硬件方案

ZUEV MPSOC 单板主要是由 SOC 处理电路、外部接口电路以及电源转换电路等组成,该板的核心处理电路以高性能 SOC 器件为核心,利用片内 ARM 硬核,逻辑资源、数字信号处理单元、片上 RAM、片外 DDR4 内存组等资源完成视频数据监控的功能。单板通过千兆以太网接口实现与外部模块进行数据交换,或是通过千兆以太网将数据下载到其他存储器件上。为了保证数据的下载,单板提供了三路千兆以太网网口,可以提供数据下载功能。电源转换电路为本模块内部的各功能电路的正常工作提供了必要的电源。

ZU4EV 芯片包含有 ARM 内核,共含有 4 核,主频可以达到 1.5G,同时还含有 ARM R5内核和 GPU 硬核等等资源。利用这些丰富的资源,可以安装 Linux 操作系统,从而获得更多的灵活性。除此之外,还可以利用 FPGA 的片上逻辑资源实现对视频数据或是监控数据进行控制、处理、存储等功能。FPGA 外部挂载 1 颗容量 256Mb 的 NOR FLASH,用作 FPGA程序 FLASH 型 号 为 S25FL256SAGMFI000。ZU4EV 芯 片 支 持 32 位 或 者 64 位 的 DDR4,LPDDR4,DDR3,DDR3L, LPDDR3 存储芯片,在 PS 端带有丰富的高速接口如 PCIE Gen2,USB3.0, SATA 3.1, DisplayPort ;同时另外也支持 USB2.0,千兆以太网,SD/SDIO,I2C,CAN,UART,GPIO 等接口。PL 端内部含有丰富的可编程逻辑单元,DSP 和内部 RAM

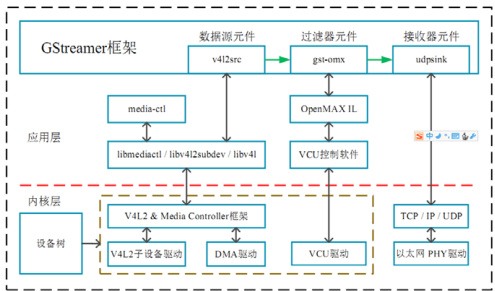

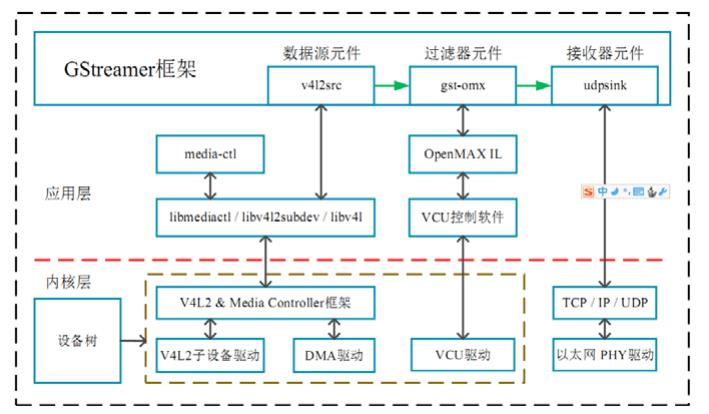

2 编码传输系统整体框架

编码传输系统的具体设计框图如图 1 所示。系统通过高速视频接口采集原始视频数据,并使用视频处理 IP 核对原始数据进行预处理,预处理后的数据以 DMA 传输方式传送到 PS端的帧缓存区中。应用软件通过驱动程序与 VCU 编码器中的 MCU 进行交互,MCU 控制VCU 编码器从原始视频数据帧缓存中获取数据并进行编码,编码后将视频比特流传回 DDR存储器。最终,软件对压缩后的视频比特流进行打包并通过网络发送。

APU 处理系统(PS) 2ynq UtrseEthernet SDDDRC SATA ComeaaAx InterconectHPO HPM0 HP1 HPCO MCU Firmware可编程逻辑(PL)AXI SmartConnect Smartconnect SmartConnect↑ 视频输入Frame Buffer Write HDMIRXEncoder : UHP-SD- RXi Video Processing Subsystem MCU ·TPG输入 T H Vieo-RX 采集 Register Space 编码 控制 数据

3 软件实现

编码传输系统采用 Linux 作为系统平台搭建软件系统。 软件设计分为内核层驱动以及应用软件,具体结构如图 2 所示。采集及预处理部分使用 V4L2 框架实现设备驱动,并采用Media Controller 辅助框架实现对各视频 IP 核的管理与配置。编码器部分采用普通字符型设备模型实现编码器驱动并提供了相应的 IOCTL 接口,VCU 控制软件通过 IOCTL 接口实现与MCU 间通信。在控制软件上层采用 OpenMAX IL 框架对编码器的底层软硬件实现进行封装并提供了标准访问接口。采集流水线、实时编码器、网络传输模块最终被实现为 GStreamer 中的 v4l2src、gst-omx、udpsink 等组件,应用程序通过组合各组件实现完整的 H.265 视频编码传输系统。

4 系统运行测试

在对整个系统进行测试前, 首先对系统的各个功能模块进行测试以确保系统各功能模块

能够正常运行。由于编码传输系统的采集、编码、网络传输相对独立,因此可以采用模块化测试对各功能模块进行独立验证。在测试过程中,先对采集、编码、网络传输部分进行了测试,最终进行系统整体测试。

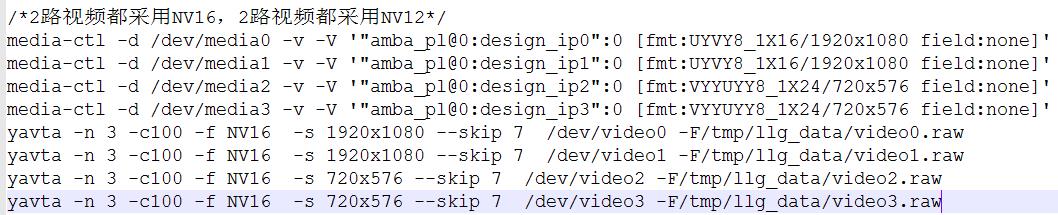

4.1 视频采集测试

视频采集通道测试使用了 media-ctl、v4l2-utils、yavta 等开源工具。media-ctl 工具用于对各 IP 核输入输出接口的参数进行配置,v4l2-ultils 用于对 Frame Buffer Writter IP 核的数据存储格式进行设置,yavta 工具用于实现数据的采集与存储。具体测试代码如图 3 所示:

测试程序将采集的原始视频数据存储为文件。本文采用 YUV 播放器对原始视频数据文件进行播放测试。根据 YUV 播放器所显示信息,视频数据参数与测试软件设置一致,说明采集通道中各 IP 核均正常工作。

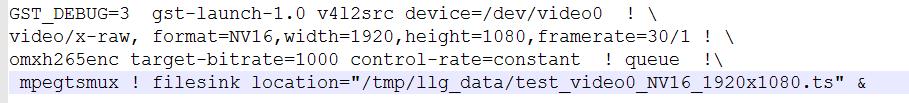

4.2 视频编码测试

视频编码测试使用GStreamer 命令行来测试。Gstreamer 可以配置编码视频的长、宽、帧率、编码方式(H264、H265 等)、码率、码率控制方式(可变码率、固定码率等)、封装方式等。其他第一路视频的gstreamer 编码命令如图4 所示:

在测试过程中,本文还对实时编码传输时自研板的 CPU 占用率进行了测试。经过多次测试与记录,板上 CPU 占用率约为 11% ,CPU 占用率较低。由此可见,编码传输系统的数据采集、编码等操作多数由硬件实现,CPU 只进行与硬件间交互、少量中间数据处理以及网络打包等操作。编码传输系统的低CPU 占用率为后续其他功能开发提供了一定的裕度。

5 结论

本文在 Zynq UltraScale+ MPSoC 平台下通过软硬件协同设计实现了视频的 H.265 编码传输系统。在该系统中,视频的采集、预处理通过对 Zynq UltraScale+ MPSoC 的可编程逻辑部分进行编程实现;视频的编码通过器件中集成的视频编解码单元硬核实现。通过硬件实现预处理和视频的编码,在提高整体性能的同时降低了系统的功耗。系统的软件设计通过采用GStreamer 框架实现,采集、编码以及网络传输实现为其中的独立组件,应用程序通过组合各组件实现完整的 H.265 视频编码与传输系统。应用程序的采集组件与编码组件间采用零拷贝技术避免了内存拷贝操作,降低了系统的CPU 资源占用。

参考文献:

[1] Bross B, Schwarz H, Marpe D. The New High-Efficiency Video Coding Standard[J]. Smpte Motion Imaging Journal, 2013, 122(4):25-35.

[2] 祁正杰 . H.265/HEVC 视频编码变换模块优化与实现 [D]. 西安电子科技大学 , 2017.

[3] 占贞强 . 嵌入式多路无线视频监控系统设计与实现 [D]. 哈尔滨工程大学, 2015

[4] 张玢 . H.264 编解码器软硬件协同设计与验证技术研究 [D]. 西安石油大学, 2011.

[5] 刘铁华 . 基于 HEVC 框架的无损压缩编码算法研究 [J]. 软件 , 2013, 34(02):69-72.

[6] 王佳惠 . H.265/HEVC 帧内编码快速率失真优化研究 [D]. 西安电子科技大学 , 2017.

[7] 叶新 . 实时超高清 HEVC 视频编码器关键模块设计 [D]. 浙江大学 , 2015.

[8] 陈飞洋 . 基于 H.265 编码的视频处理系统设计 [D]. 成都理工大学 , 2017.

[9] 贾开元 . 高效视频编码 HEVC/H.265 中新型变换的研究 [D]. 电子科技大学 , 2017.

[10] 孙振华 . 基于D-Bus 的高清视频会议终端的设计与实现[D]. 华南理工大学,2012.

[11] 梁钟保 . 高清视频会议终端中的监控管理子系统的设计与实现 [D]. 华南理工大学 ,2012.

[12] 蓝国民 . 高清视频会议终端云台控制的设计与实现[D]. 华南理工大学,2014

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)